### Rekonfigurierbare Architekturen für HPC

Viktor Achter (RRZK), Florian Mayer (FAU)

Assoziierter Partner: Intel Deutschland GmbH

### Motivation / Ziele

- Erweiterung der technologischen Alternativen für HPC

- Acceleratoren sind eine effektive Alternative zu CPUs

- Pro: höhere Effizienz bei passender Problemstellung

- Cons: hoher Spezialisierungsgrad

- → möglichst große Auswahl unterschiedlichster Hardware Architekturen -Auswahl passend zur Problemstellung

- Reduktion der Einstiegshürden

- Einstiegshürde zu diversen Beschleunigern gering, wenn diese mit OpenMP genutzt werden können.

- OpenMP Pragmas Standard in HPC.

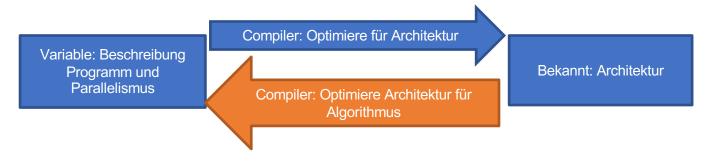

### Optimierungsprobleme

Normaler Compiler:

Variable: Beschreibung

Programm und

Parallelismus

Compiler: Optimiere für Architektur

Bekannt: Architektur

ORKA-HPC Framework:

### Überblick Arbeitspakete

**High Performance Computing**

5.2 AP1 Optimierte Source-to-Source Transformation von OpenMP-Pragmas 5.1 1.4 AP5 2.2 4.3 4.1 4.3 3.4 3.3 Demonstratoren für Funktionalität, 1.2 5.3 1.1 1.5 AP6 Projektmanagement 5.4 und Qualitätskontrolle AP4 Schnittstellen und Optimierung Opt 1.2 Leistung, AP3 Partielle AP2 Low-Level-Plattform Rekonfigurierbarkeit 3.3

### AP2+3 Low Level Platform

### Bereitstellung: Low Level Plattformen

#### **Anforderungen:**

- Unterstützung einer repräsentativen FPGA-Karte

- Xilinx, Altera

- Erstelle LL-Plattformen mit Optimierungen für unterschiedliche Code Charakteristiken

- Maximale Speicherbandbreite

- Cache

- Streaming

- Jeweils optional mit Softcore und Debugging Funktionen

- Partielle Rekonfiguration

- Nutzung größerer Chipflächen vs. Reprogrammierungszeiten

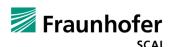

### Umfangreiches Design mit softcore Prozessor, Debugging, etc..

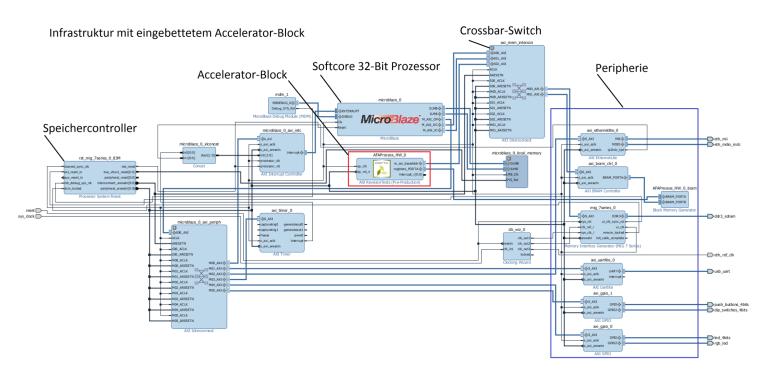

### Minimalistisches Design mit Speicherinterface und Pcie

ORKA-HPC

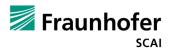

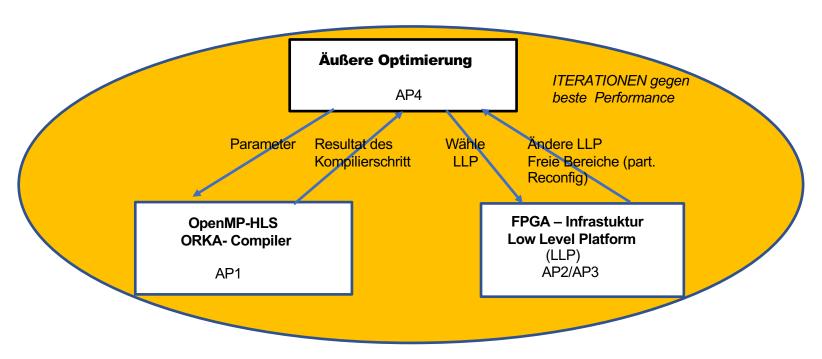

# AP4 Schnittstellen und Optimierung

### **Optimierung**

SPONSORED BY THE

12

### Unterstützung Laufzeitumgebung

- Informationsschnittstelle

- 1te Dokumentation und Schnittstellendefinition

- Runtime Library in Arbeit

SPONSORED BY THE

13

### **AP 5 Demonstrator Suite**

Assoziierter Partner: Intel Deutschland GmbH

### **Demonstrator Application Suite**

#### Anforderungen und Anwendungsfälle:

- Representation von Rechenmustern und OpenMP Annotationen

- HPC und Data Analytic Workloads

- Compute und Kontrollflüsse

- Demonstration von FPGA-bezogenen Optimierungen

- Variable Repräsentation von Fixed und Floating-Point Daten über IEEE Standards hinaus (Double, Single, Half-Precision)

- Ressourcen Optimierung

- Benchmarking und Qualitätssicherung

- Mini-App und Kerneltypen von Demonstratoren

- Performance und Ressourcennutzungs-Benchmarks

- Referenzimplementierung auf CPUs und GPUs unter Nutzung von State-of-the-Art Features (e.g. SIMD, Multi-threading)

### Beispielanwendungen und Kernels

**High Performance Computing**

| Code / Domain                         | OpenMP Feature                                                                                                                     | Anzahl                               | Anmerkungen                      |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------|

| SWCluster / Ising<br>Model            | omp parallel omp for [collapse] omp parallel for [collapse] omp parallel for reduction(+) omp [parallel] simd [for] [reduction(+)] | (2x)<br>(2x)<br>(2x)<br>(1x)<br>(3x) | CPU: C++<br>GPU: CUDA            |

| AMGmk (CORAL) /<br>Solver             | OpenMP code but no OpenMP 4.0 / 4.5 features                                                                                       |                                      | Platzhalter für SCAI AMG solver  |

| DM-HEOM Kernel / open quantum systems | omp parallel for omp simd                                                                                                          | (17x)<br>(7x)                        | CPU: C++ / OpenCL<br>GPU: OpenCL |

| Genomics:<br>Deduplication            |                                                                                                                                    |                                      | Variable Datenrepräsentation     |

| Deep Learning Kernel<br>Suite         |                                                                                                                                    |                                      | kompakte DL Kernel               |

| HLS Kernels                           |                                                                                                                                    |                                      | Performance-Vergleich            |

### AP1 - Optimierte Source-to-Source Transformation von OpenMP-Pragmas

### Stand der Kunst

**High Performance Computing**

```

C-Code

```

```

for (int i=0; i<n; ++i) {

if (cond(i)) {

a[i] = 1;

}

b[i] = 0;

}</pre>

```

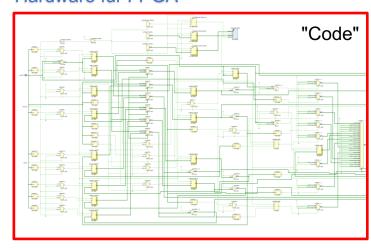

**FPGA**

"Code"

Infrastruktur

### Stand der Kunst

Umprogrammierung

**High Performance Computing**

```

FPGA

C-Code

for (int i=0; i<n; ++i) {

Mehrschrittige

"Code"

if (cond(i)) {

Werkzeugkette

a[i] = 1;

b[i] = 0;

Stellschrauben

Timing

```

Trial & Error – "Tuning"

Infrastruktur

- Schaltung zu groß für FPGA

- Schaltung zu langsam für

Federal Ministry and Research

#### C-Code

```

for (int i=0; i<n; ++i) {

if (cond(i)) {

a[i] = 1;

}

b[i] = 0;

}</pre>

```

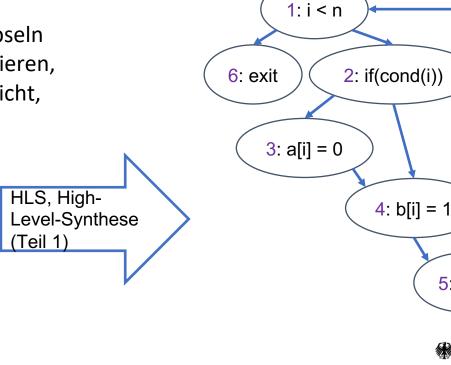

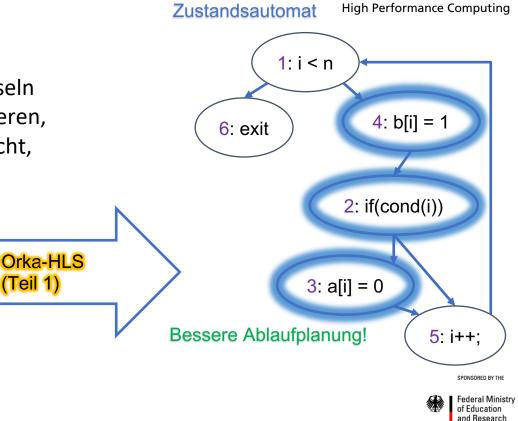

## orkat

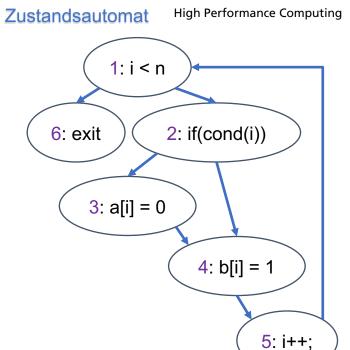

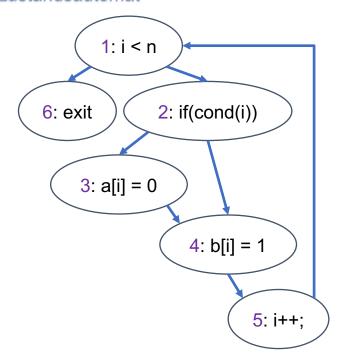

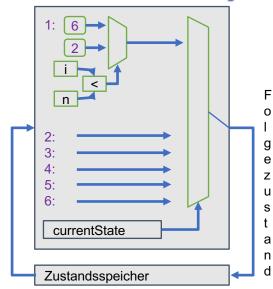

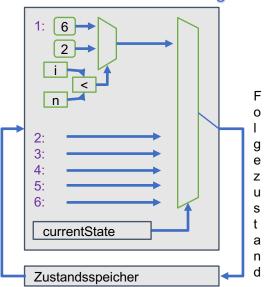

#### Zustandsautomat

VHDL – Abstrakte High Performance Computing Hardware-Beschreibung

## VHDL-Synthese Logik-Synthese Logik-**Optimierung** etc.

**High Performance Computing**

#### Netzliste – Konkrete Hardware für FPGA

### Übertragung von Cauf OpenMP

```

OpenMP-Code

```

```

#pragma omp target fpga1

#pragma omp parallel for

#pragma omp simd

for (int i=0; i<n; ++i){

if (cond(i)){

a[i] = 1;

}

b[i] = 0;</pre>

```

FPGA

"Code"

Interface

Infrastruktur

#### OpenMP-Code

```

#pragma omp target fpga1

#pragma omp parallel for

#pragma omp simd

for (int i=0; i < n; ++i) {

if (cond(i)) {

a[i] = 1;

b[i] = 0;

```

OpenMP-Compiler

omp initialiHigh Performance Computing omp outlined(&n); void omp outlined(...) { make threads(); run threads ( loopBody);

destroy threads();

for (...) {...}

void loopBody(...) {

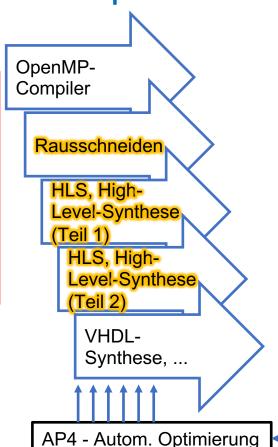

AP1: Zusammensuchen der verstreuten Code-Stücke, die der OpenMP-Compiler für das pragma-Beispiel produziert.

```

OpenMP-Code

```

```

#pragma omp target fpga1

#pragma omp parallel for

#pragma omp simd

for (int i=0; i<n; ++i) {

if (cond(i)) {

a[i] = 1;

}

b[i] = 0;

}</pre>

```

OpenMP-Compiler

AP1: Zusammensuchen der verstreuten Code-Stücke, die der OpenMP-Compiler für das pragma-Beispiel produziert.

\_\_omp\_initialiHigh\_Performance(Gryphuting \_\_omp\_outlined(&n); } void \_\_omp\_outlined(...) {

make threads();

void lo

\_\_destroy\_threads();

run threads ( loopBody);

Rausschneiden

Federal Minist of Education and Research

5: i++;

SPONSORED BY THE

and Research

#### Kommerzielle HLS-Werkzeuge:

- können nicht mit den vielen Code-Schnipseln umgehen, die OpenMP-Compiler produzieren,

- kennen das Datenabhängigkeitswissen nicht,

```

#pragma omp target fpga1

#pragma omp parallel for

#pragma omp simd

for (int i=0; i<n; ++i){

if (cond(i)){

a[i] = 1;

}

b[i] = 0;

}</pre>

```

Zustandsautomat

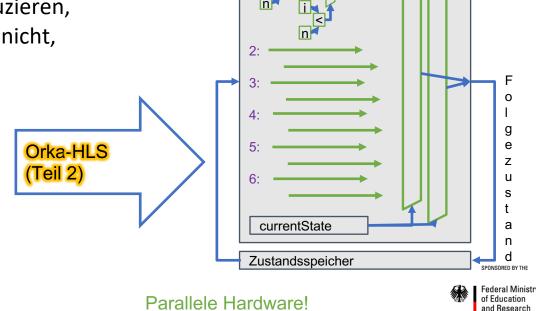

#### Kommerzielle HLS-Werkzeuge:

- können nicht mit den vielen Code-Schnipseln umgehen, die OpenMP-Compiler produzieren,

- kennen das Datenabhängigkeitswissen nicht,

(Teil 1)

```

pragma omp target fpga1

#pragma omp parallel for

#pragma omp simd

for (int i=0; i < n; ++i) {

if (cond(i)) {

a[i] = 1;

b[i] = 0;

```

#### Kommerzielle HLS-Werkzeuge:

- können nicht mit den vielen Code-Schnipseln umgehen, die OpenMP-Compiler produzieren,

- kennen das Datenabhängigkeitswissen nicht,

- verstehen #pragmas nicht.

```

#pragma omp target fpgal

#pragma omp parallel for

#pragma omp simd

for (int i=0; i<n; ++i) {

if (cond(i)) {

a[i] = 1;

}

b[i] = 0;

}</pre>

```

#### VHDL – Abstrakte Hardware-Beschreibung

#### Kommerzielle HLS-Werkzeuge:

- können nicht mit den vielen Code-Schnipseln umgehen, die OpenMP-Compiler produzieren,

- kennen das Datenabhängigkeitswissen nicht,

- verstehen #pragmas nicht.

```

#pragma omp target fpga1

#pragma omp parallel for

#pragma omp simd

for (int i=0; i<n; ++i) {

if (cond(i)) {

a[i] = 1;

}

b[i] = 0;

}</pre>

```

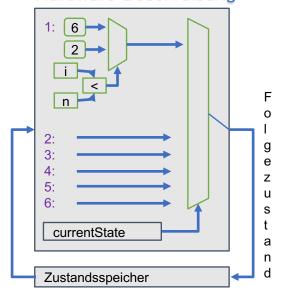

1: 6

#### Kommerzielle HLS-Werkzeuge:

- können nicht mit den vielen Code-Schnipseln umgehen, die OpenMP-Compiler produzieren,

- kennen das Datenabhängigkeitswissen nicht,

- verstehen #pragmas nicht.

```

#pragma omp target fpga1

#pragma omp parallel for

#pragma omp simd

for (int i=0; i<n; ++i) {

if (cond(i)) {

a[i] = 1;

}

b[i] = 0;

}</pre>

```

#### AP1:

- Technischer Durchstich des

- Orka-HLS Frameworks

- Einfache Bit-Optimierung

- SDC-Ablaufplanung

- Interface Generators

- uvm.

### **Status**

**High Performance Computing**

- Technischer Durchstich vom Kompilat zum laufenden FPGA Bitstream

- Diverse Schnittstellendiskussionen mit Partnern und den anagestrebten HLS Herstellern

- Erste Low-Level-Plattformen erstellt sowie verskriptet

- Erste Beschreibung von Runtime Library Schnittstellen erstellt

- Einige Beispielcodes bestimmt und in Teilen vorbereitet

- Erste Version des Treibers für die Host-FPGA Kommunikation vorbereitet

- Für den Durchstich wurde eine teilfunktionale ORKA-HLS (ZIB, FAU) erstellt

### Vielen Dank!

**High Performance Computing**

- RRZK

- Prof. Dr. Ulrich Lang

- Viktor Achter

- Lech Nieroda

- FhG SCAL

- Horst Schwichtenberg

- Olga Rodikow

- Fridrich-Alexander Universität Erlangen (FAU)

- Prof. Dr. Michael Philippsen

- Florian Mayer

#### Konrad Zuse Institut

- Dr. Thomas Steinke

- Marius Knaust

- Unterauftragnehmer / Assoziierte Partner

- Jesko Schwarzer

- Dr. Michael Klemm (Intel Deutschland GmbH)